#### Low-Stress Silicon Cladding for Surface Finishing Large UVOIR Mirrors NASA

SBIR Phase II contract No. NNX14CP14 Technical Monitor: Dr. David Redding (JPL)

PI: David A. Sheikh

ZeCoat Corporation

11/20/2014

#### Introduction

- In this presentation, I will discuss the status of our Phase II silicon cladding development effort, which is based on ion-assisted, physical evaporation (PV)

- The coating area is currently 1.2-meter in diameter and we are considering options for demonstrating coating a larger area (2-meter +)

- Future large telescopes may be monolithic (4-meters or larger), or comprised of many smaller segments (~1.5-m).

### What is Silicon Cladding?

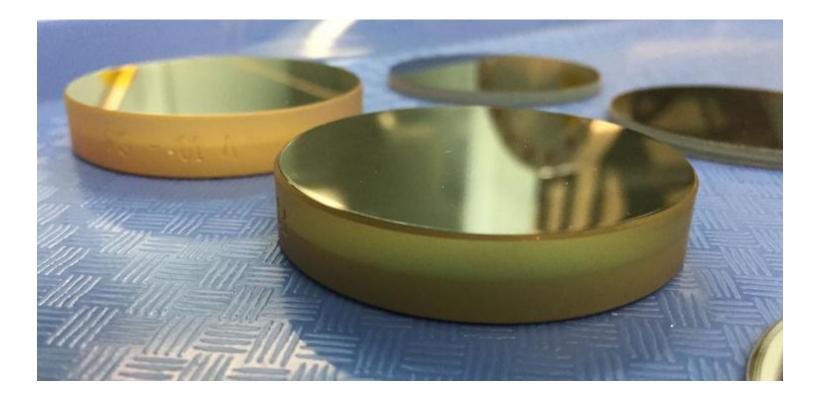

- Silicon cladding is a material applied on the surface of a SiC mirror substrate, to provide a better surface to polish and to reduce figuring time

- A 10 to 100-micron silicon layer is typically applied on top of the SiC

- Why Silicon? Good material to diamond turn or polish, and the CTE is very close to SiC

#### Research Goals

- Create a viable cladding production process for large mirrors

- Create a process that is scalable to ANY size vacuum chamber

- Create a "turn-key" technology suitable for licensing to silicon carbide mirror manufacturers

- ZeCoat 2<sup>nd</sup> source supplier

- ZeCoat R&D

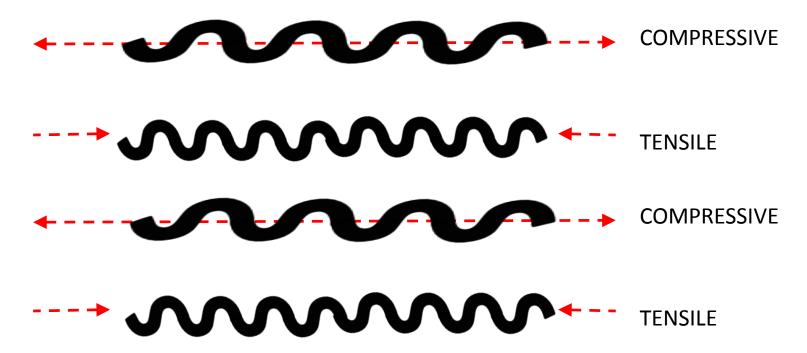

ZeCoat's Si cladding process is based on periodically alternating the sign of the coating stress to yield a near-zero net coating stress. IAD silicon has compressive stress and non-IAD silicon has natural tensile stress

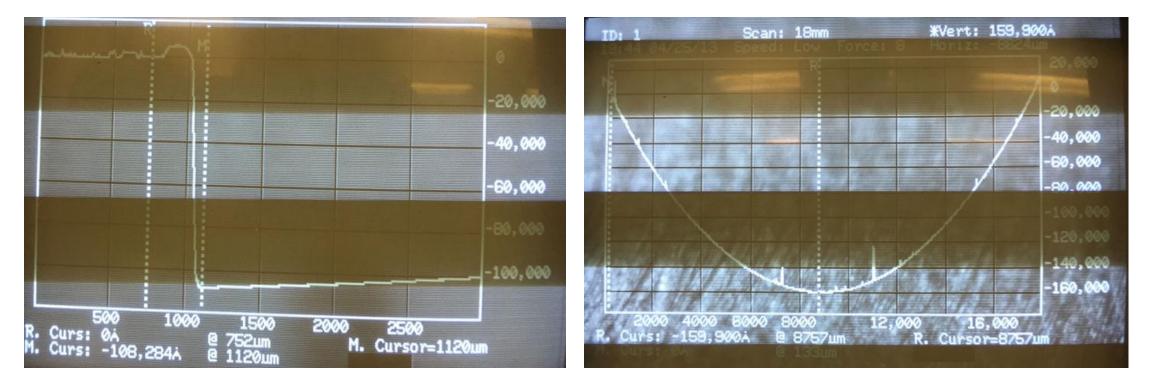

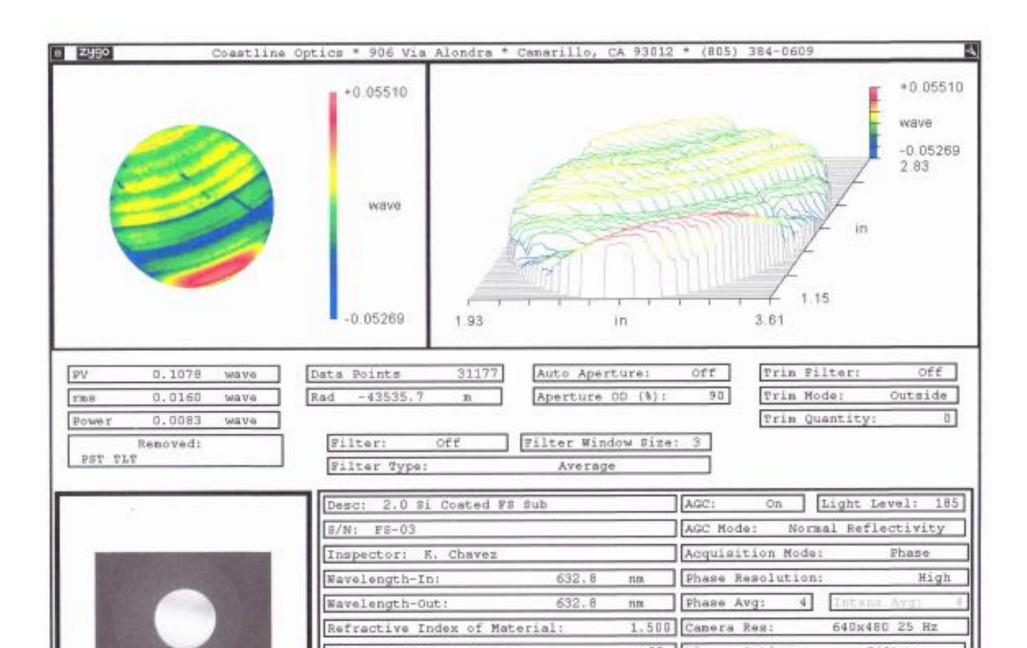

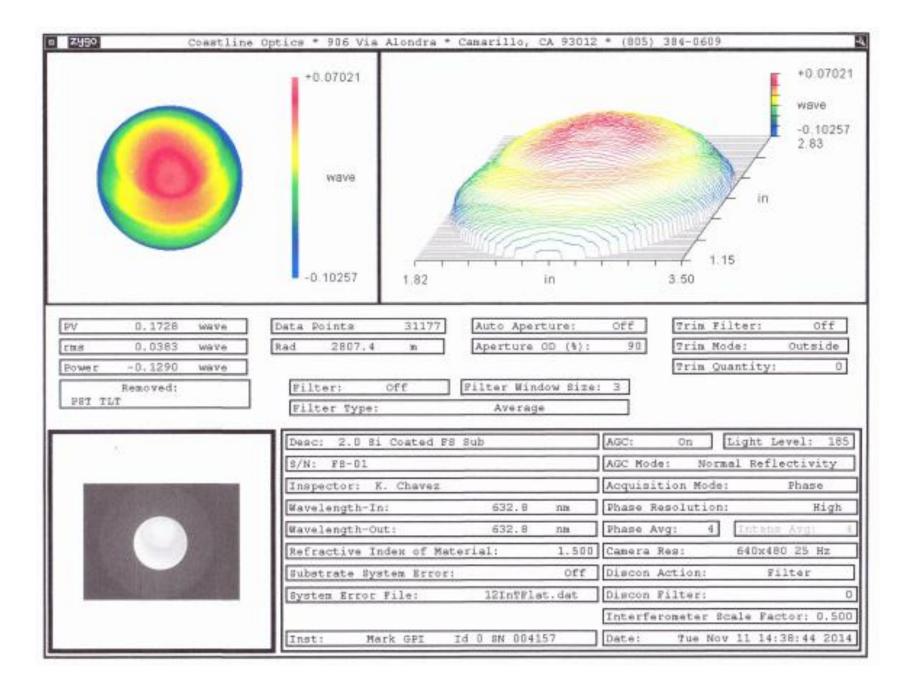

## Calculating Stress (goal is less than 85 MPa)

Profilometry measurement shows ~11 microns of Si

1 inch diameter, 20-mil fused silica disc bent 16-microns = ~60 MPa (tensile)

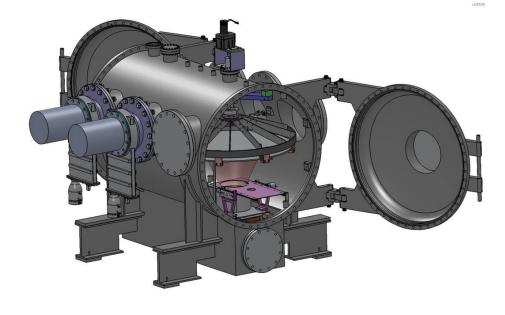

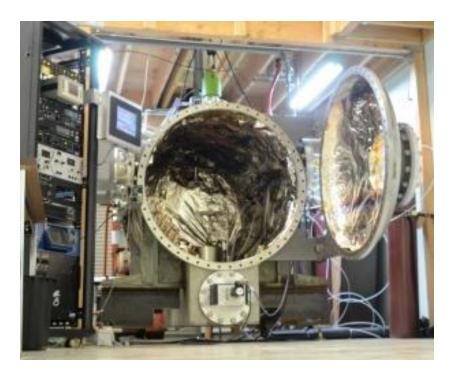

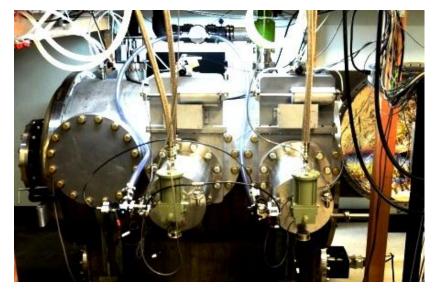

ZeCoat's 1.2-m vacuum coating chamber was completed in March, 2013 and utilizes an ion-assisted e-beam evaporation system

# Phase I & II Challenges

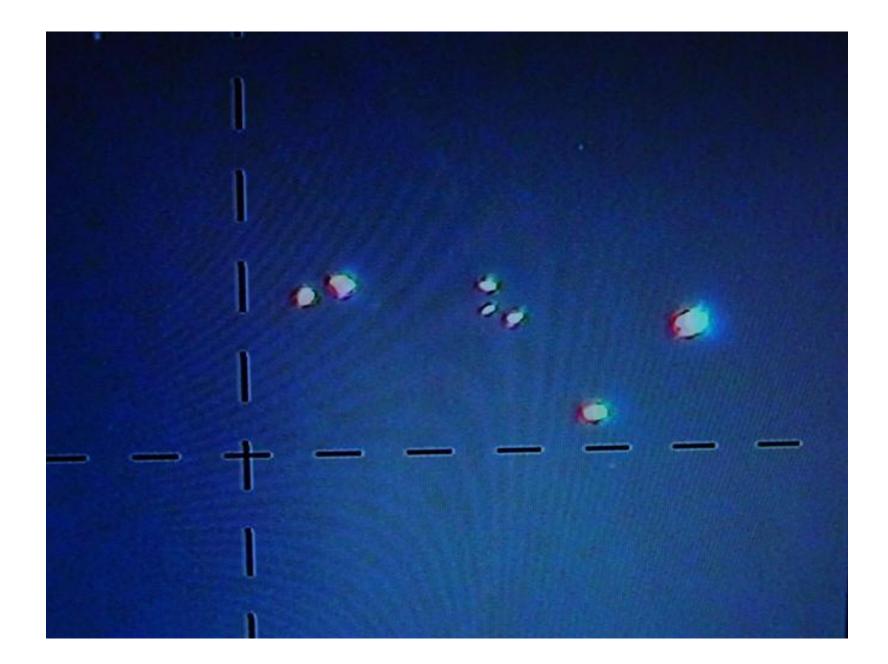

- Surface defects

- A spitting event is when molten silicon explodes from the evaporation crucible potentially damaging the silicon clad surface.

- Pre-conditioning

- Excessive evaporation rates, e-beam "digging"

- Dust; opening and closing the chamber many times during the process to replenish materials, etc.

- Arcing

- Arcs associated with ebeam evaporation (high voltage discharges within the chamber) cause many problems

# **Overcoming Arcing Problems**

- Designed and installed new shielding over the electron emitter assembly

- New shielding over ceramic insulators

- Ground wires far from high-voltage lines

- Installed relays between the computer system and process sensors within the chamber, to isolate the computer from arcing interference

- Wrote new motion control software to detect false signals due to arcing and reset the computer system seamlessly

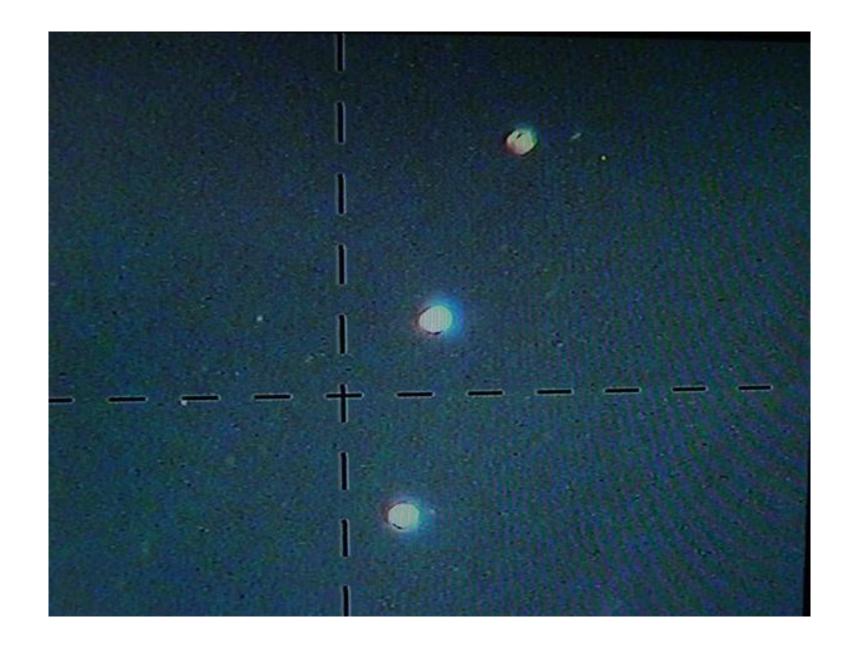

### Silicon Polishing Tests

## Polishing Results Phase I and Phase 2 (1<sup>st</sup> Q)

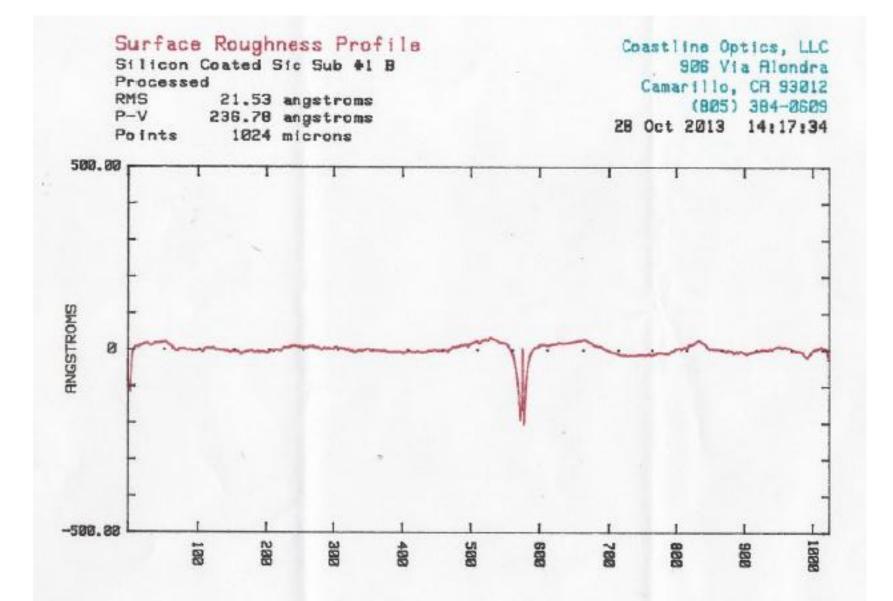

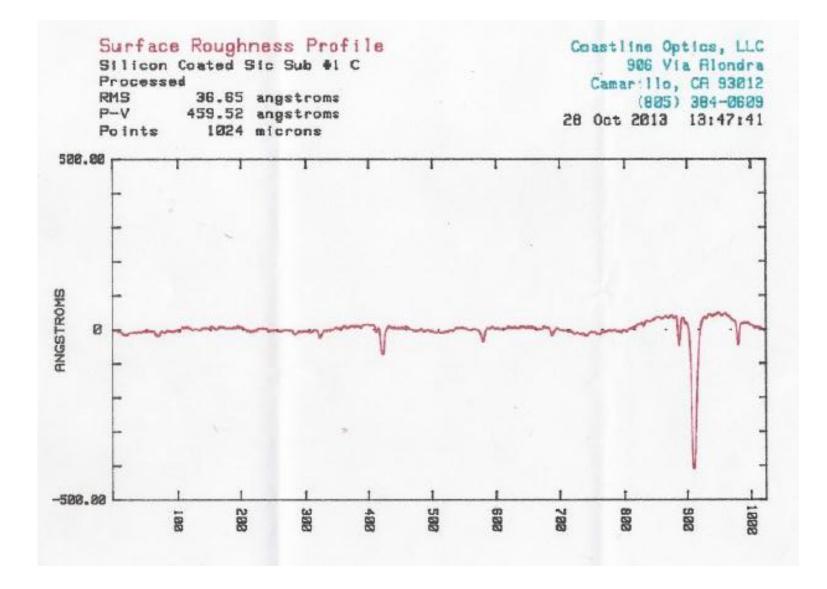

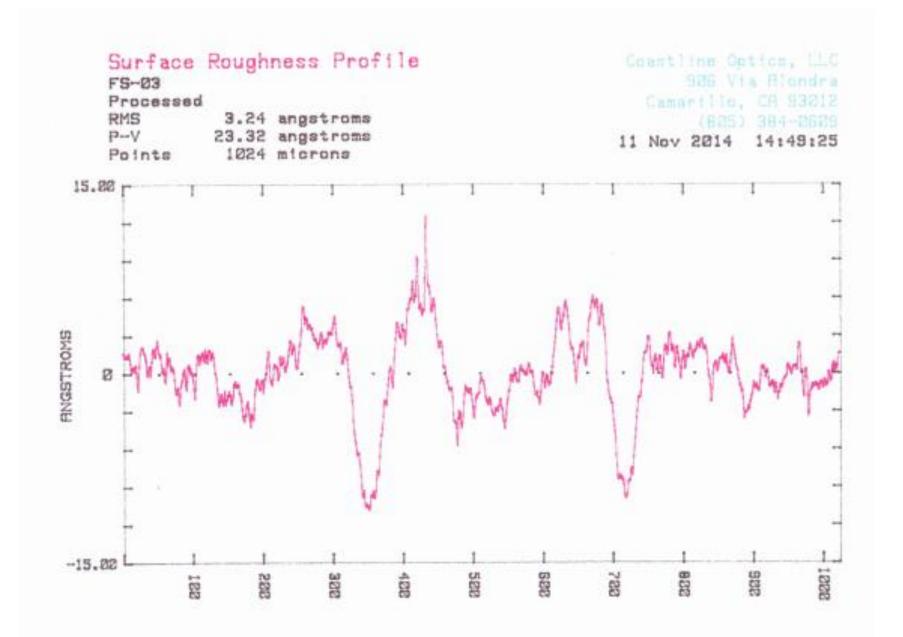

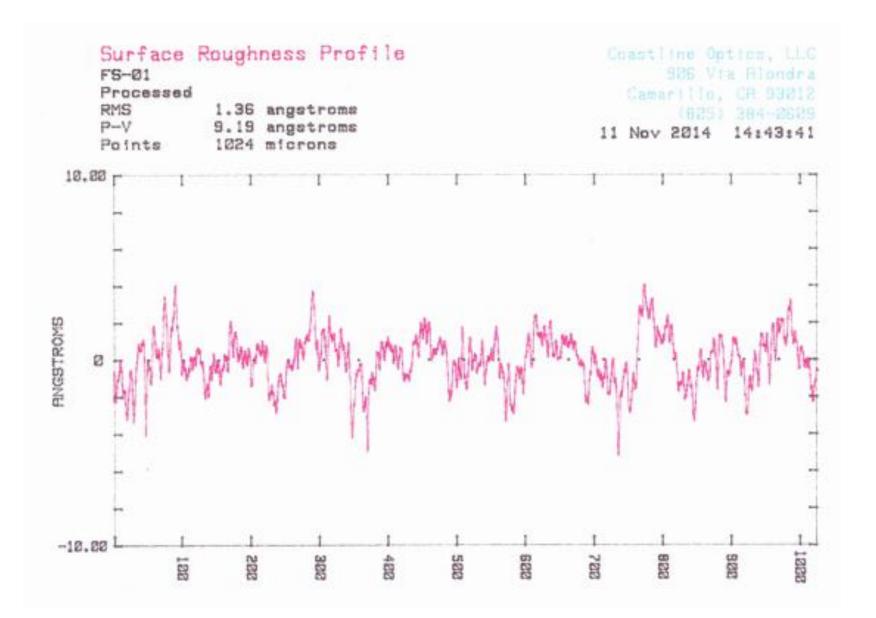

| Scan lengt | h 1024 | microns                 |            |                  |         |          |

|------------|--------|-------------------------|------------|------------------|---------|----------|

|            |        |                         |            |                  |         | goal < 5 |

| Project    | ID     | Substrate               | Evap. Rate | Si Thickness (µ) | PTV (A) | RMS (A)  |

| Phase I    | 1a     | SiC (rough)             | Зx         | 20               | 16      | 2.8      |

| Phase I    | 1b     | SiC (rough)             | Зx         | 20               | 236     | 21.5     |

| Phase I    | 1c     | SiC (rough)             | Зx         | 20               | 460     | 36.7     |

| Phase I    | 2a     | SiC (rough)             | Зx         | 20               | 137     | 21.4     |

| Phase I    | 2b     | SiC (rough)             | Зx         | 20               | 84.2    | 10.8     |

| Phase I    | 2c     | SiC (rough)             | Зx         | 20               | 314.1   | 24.4     |

| Phase II   | SN1    | Fused Silica (polished) | 1x         | 4                | 9.2     | 1.4      |

| Phase II   | SN3    | Fused Silica (polished) | 1x         | 11               | 23.3    | 3.2      |

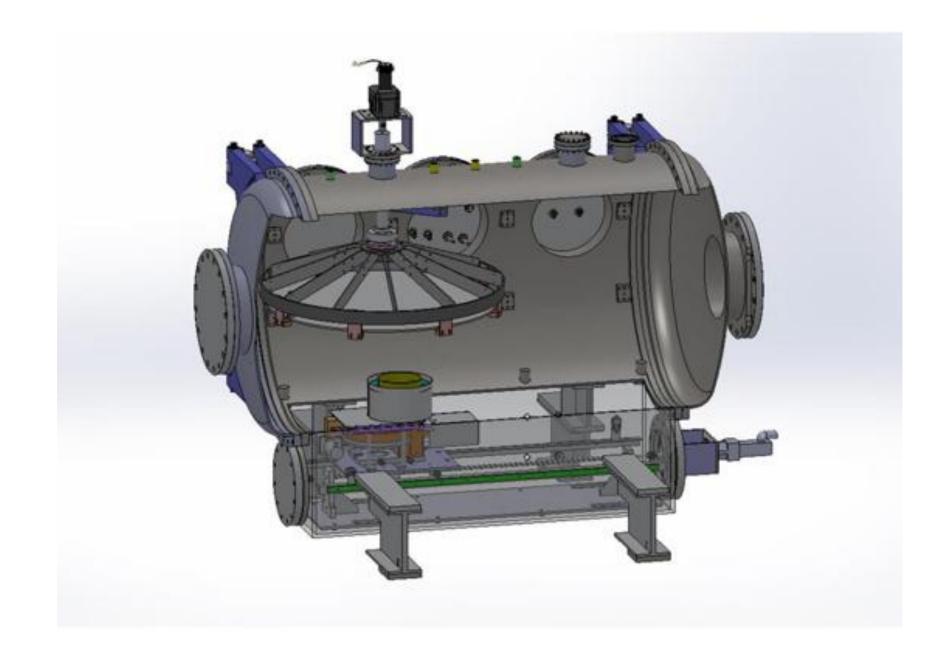

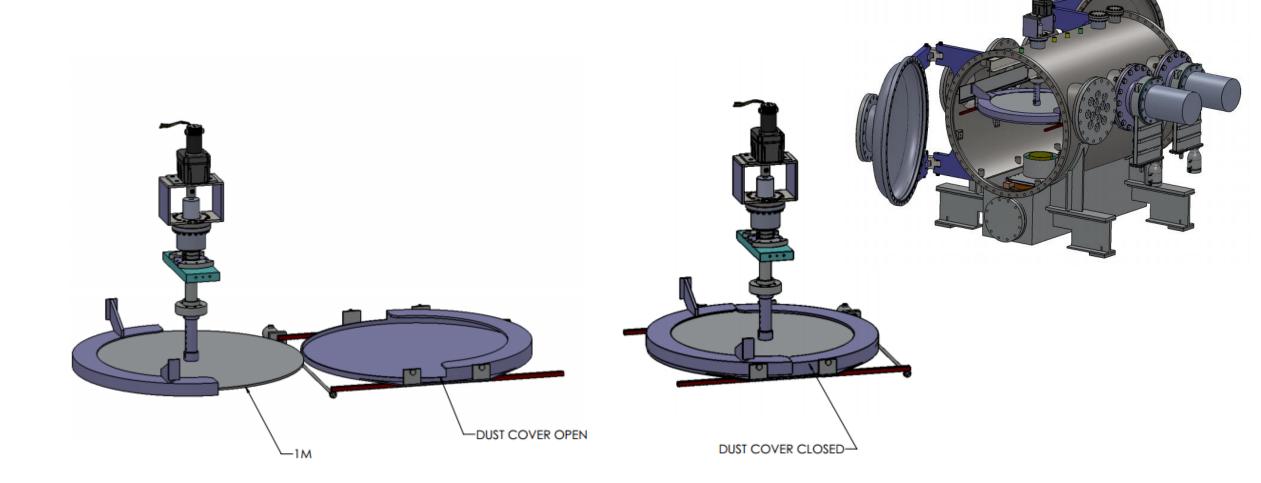

#### Motorized Dust Cover Inside Vacuum Chamber

Alternatives to heating with an electron beam? Possible advantages (higher rates?, reduced surface defects?)

Resistive graphite heating (3000 C)

Thermal resistive Ta source (1800 C)

Inductive heating

# Other things to investigate?

- Cold-cathode neutralization of the ion gun?

- Process duration is currently limited because of required ion gun maintenance (neutralization filament replacement)

- More automation

- Rate control

- Automate ion gun turning on off

- Crucible changes (heat up and cool down)

- How to remove the silicon for re-work?

- Chemical removal

- Micro-gritblasting

#### Questions?